List of Selected Publications by Research Topics

List of Selected Publications by Research Topics

Data Converters

1. 2016 (IEEE TCAS-I) An embedded passive gain technique for asynchronous SAR ADC achieving 10.2 ENOB 1.36-mW at 95-MS/s in 65 nm CMOS

2. 2018 (IEEE JSSC) A 12-bit 1.6, 3.2, and 6.4 GS/s 4-b/cycle Time-Interleaved SAR ADC with Dual Reference Shifting and Interpolation

3. 2020 (IEEE JSSC) A 12.8-Gbaud ADC-based Wireline Receiver with Embedded IIR Equalizer

Cryogenic Quantum Computing Projects

1. 2023 (IKEEE) CMOS Interconnect Electronics Architecture for Reliable and Scalable Quantum Computer

2. 2023 (IEEE ACCESS) Analysis of Quarter Method Applied ROM-based DDFS Architecture

3. 2024 (IEEE TCAS-II) A 4.3 GS/s Time-Interleaved ∆Σ DAC with temperature-insensitive bias and Harmonic cancellation for Qubit Control

4. 2024 (IKEEE) Measurement set-up for CMOS-based integrated circuits and systems at cryogenic temperature

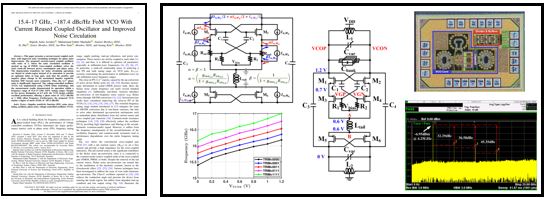

5. 2025 (TCAS-I) 15.4-17 GHz -187.4dBc/Hz FoM VCO with Current Reused Coupled Oscillator and Improved Noise Circulation

PUF Integrated Circuits and Systems for Security Projects

1. 2022 (IEEE ACCESS) Compact SRAM-Based PUF Chip Employing Body Voltage Control Technique

2. 2022 (Electronics) Stochastic Cell- and Bit-Discard Technique to Improve Randomness of a TRNG

3. 2023 (IEEE TCAS-II) High-speed Light Detection Sensor for Hardware Security in Standard CMOS Technology

4. 2024 (Electronics) A Reconfigurable SRAM CRP PUF with High Reliability and Randomness

5. 2024 (Sensors) A lightweight and high yield CMOS TRNG with lightweight Photon post-processing

6. 2024 (IEEE Transactions) Reconfigurable SRAM-based PUF (Submitted)

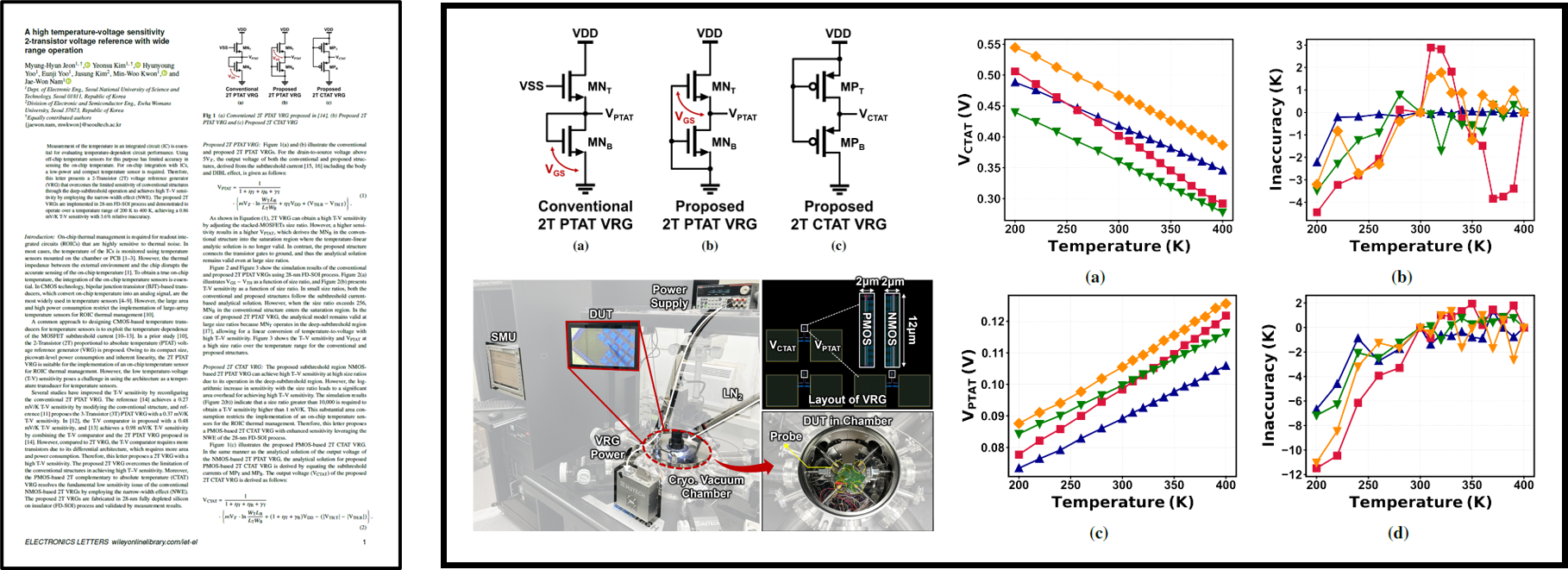

7. 2026 (Electronics letters) A high temperature-voltage sensitivity 2-transistor voltage reference with wide range operation

AMS Design Automations Projects

1. 2022 (Electronics) Regression Model-Based AMS Circuit Optimization Technique Utilizing Parameterized Operating Condition

2. 2023 (IEEE ACCESS) AMS Circuit Design Optimization Technique Based on ANN Regression Model with VAE Structure (Editor's Selected paper)

Big Data Sciences

1. 2024 (Applied Sciences) Solving Optimal EV Chargers Deployment Problem

List of All Journal Publications (After joining SEOULTECH)

List of All Journal Publications (After joining SEOULTECH)

Submitted

Submitted

Previous Publications [J01~J09]

Previous Publications [J01~J09]J.-W. Nam, and M.-W. Chen, “A 12.8-Gbaud ADC-based Wireline Receiver with Embedded IIR Equalizer,” IEEE J. Solid-State Circuits, vol. 55, no. 3, pp. 557 - 567, Mar. 2020.

J.-W. Nam, M. Hassanpourghadi, A. Zhang, and S.-W. M. Chen, “A 12-bit 1.6, 3.2, and 6.4 GS/s 4-b/cycle Time-Interleaved SAR ADC with Dual Reference Shifting and Interpolation,” IEEE J. Solid-State Circuits, vol. 53, no. 6, pp. 1765-1779, Jun. 2018

J.-W. Nam, and S.-W. M. Chen, “An embedded passive gain technique for asynchronous SAR ADC achieving 10.2 ENOB 1.36-mW at 95-MS/s in 65 nm CMOS,” IEEE Trans. Circuits Syst. I, Reg. Papers, vol. 63, no. 10, pp. 1628 - 1638, Oct. 2016.

J.-W. Nam, Y.-D. Jeon, Y.-K. Cho, J.-K. Kwon, “A 12-Bit 200-MS/s pipelined A/D converter with sampling skew reduction technique,” Elsevier Microelectronics Journal, no. 11, vol. 42, pp. 1225-1230, Nov. 2011.

Y.-D. Jeon, J.-W. Nam, K.-D. Kim, T. M. Roh, and J.-K. Kwon, “A dual-channel pipelined ADC with sub-ADC based on flash–SAR architecture,” IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 59, no. 11, pp. 741–745, Nov. 2012.

H. B. Le, J.-W. Nam, S.-T. Ryu, and S.-G. Lee, “Single-chip A/D converter for digital microphones with on-chip preamplifier and time-domain noise isolation,” Electronics Letter, vol. 45, no. 3, pp. 151-153, 2009.

Y.-K. Cho, Y.-D. Jeon, J.-W. Nam, and J.-K. Kwon, “A 9-bit 80 MS/s successive approximation register analog-to-digital Converter with a capacitor reduction technique,” IEEE Trans. Circuits Syst. II, Exp. Briefs, vol. 57, no. 7, pp. 502–506, Jul. 2012.

Y.-K. Cho, Y.-D. Jeon, J.-W. Nam, and J.-K. Kwon, “A 10-bit 30-MS/s successive approximation register analog-to-digital converter for low-power sub-sampling applications,” Elsevier Microelectronics Journal, vol. 42, no. 12, pp. 1335–1342, Jul. 2011.

Y.-D. Jeon, Y.-K. Cho, J.-W. Nam, S. -C, Lee, and J.-K. Kwon, “A 1.2 V 12 b 60 MS/s CMOS analog front-end for image signal processing applications,” Elsevier ETRI Journal, vol. 31, no. 6, Dec. 2009.